VHDL

VHDL

VHDL é uma linguagem de descrição de hardware que herda algumas convenções, atribuições de linguagens de programação c-like. VHDL permite que você modele eventos que ocorrem em função do tempo. VHDL é uma linguagem muito útil para descrever hardware porém mantendo uma distância maior de abordagem aos problemas que estão ligados a sínteze de hardware. A parte de sínteze é por conta do VHDL que constroi a parte mais baixo nível.

Ferramentas

Uma boa ferramentas para se começar a sintetizar hardware em FPGA's como as da Altera, é o Quartus Web Edition https://www.altera.com/download/ é gratuíta e fácil de se instalar. É também portada para Linux/Unix e Windows, eu aconselho a versão 32 bits apesar de nunca ter tido problema com a versão 64 bits e até mesmo abrindo projetos 32 bits no Quartus 64 bits. Algumas funções que para quem trabalha realmente em projeção de hardware, não estão disponíveis no Quartus Web Edition, mas são coisas específicas que talvéz nem faça falta para a abordagem do pessoal do LabMacambira. No entanto, comprando uma placa da Altera, tipo Cyclone II acredito que o software Quartus Edição Completa, acompanha o pacote. E uma placa dessas custa em torno de 500 dólares. Existem maneiras de se comprar pela Universidade e reduzir esse preço. De qualquer maneira Universidades geralmente tem um conjunto de placas FPGA's em laboratórios de sínteze de hardware. Outro Software é o ModelSim Altera, que também é gratuíto pelo mesmo link, e de extrema importância na sinteze de hardware. Uma vez que não tem como um hardware mais complexo, sintetizado em alto nível passar sem antes for executada uma bateria de testes pesada sobre ele para que ele realmente de todos os erros para que sejam corrigidos após Testes e Validações.

Outra ferramenta que eu recomendo fortemente é o Sigasi http://www.sigasi.com/, um plugin para Eclipse. Na verdade é uma ferramenta poderosa para descrever em VHDL. Ela é gratuíta para estudantes universitários, basta se cadastrar colar o link na sessão de updates de plugins no Eclipse, instalar e programar em VHDL de uma maneira muito mais prática. Eu recomendo o Sigasi, pois VHDL é uma linguagem bastante propensa a erros de sintaxe.

Altera FPGAs

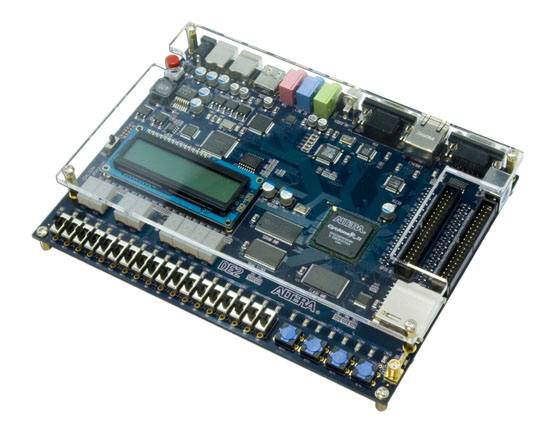

A Altera faz fpgas, asics. Fpgas são placas com circuito mapeados para se combinar sob demanda da descrição VHDL que será programada na FPGA com a ajuda do Quartus. As placas da ALTERA(R) Cyclone 2 são bastante robustas e eficazes vale a pena comprar uma para efetuar testes, estudar.

Duas FPGAS que recomendo são C6 e C7.

Part Number EP2C35F672C6 Description IC CYCLONE II FPGA 672FBGA

http://www.buyaltera.com/scripts/partsearch.dll?Detail&name=544-1087-ND

Part Number EP2C35F672C7 Description IC CYCLONE II FPGA 672FBGA

http://www.buyaltera.com/scripts/partsearch.dll?Detail&name=544-1088-ND

Cyclone 2 Handbook

http://www.altera.com/devices/fpga/cyclone2/cy2-index.jsp

Nios(R) II

Nios is a soft processor that can be incorporated in systems implemented on an FPGA device by using the Qsys System Integration tool or the SOPC Builder tool.

Padrões de Projeto

Um padrão de projeto em VHDL é BC-BO. Onde se cria um BC.VHDL e um BO.VHDL além das subpartes que provavelmente serão criadas para compor esses dois. Um exemplo de projeto de um multiplicador https://gist.github.com/tonussi/5822655 utilizando BC-BO.

Temas para Projetos Práticos de Sistemas Digitais

1. SAD Cálculo da soma das diferenças absolutas entre os pixels de duas imagens. Há uma matriz de nxn pixels, armazenados em uma memória (M1) e uma matriz de nxn pixels, armazenados em uma outra memória (M2). Deve ser calculada a diferença absoluta entre os pixels das duas imagens, par a par. O resultado é acumulado em um registrador e mostrado ao final do cálculo. M1 e M2 devem ser internas ao FPGA. Considerar que cada pixel está codificado com 8 bits.

2. Compensador de Movimento Recebe o valor de dois vetores de movimento (valores inteiros) e acessa uma memória onde está armazenado um bloco de nxn pixels (bloco de referência). Com base nos pixels do bloco de referência e nos vetores de movimento, remonta um bloco. Há duas memórias: M1, que armazena o bloco de referência, e M2, na qual deve ser escrito o bloco remontado. Ambas memórias devem poder armazenar nxn pixels. Considerar que cada pixel está codificado com 8 bits.

3. Detector de Bordas Recebe o valor de uma máscara (matriz 3x3 de inteiros) e acessa uma memória onde está armazenado um bloco de nxn pixels (imagem de referência). Com base nos pixels da imagem de referência e na máscara, remonta uma imagem com cada pixel multiplicado pela máscara. Há duas memórias: M1, que armazena a máscara de referência, e M2, na qual deve ser escrita imagem processada. Ambas memórias devem poder armazenar nxn pixels. Considerar que cada pixel está codificado com 8 bits.

4. Multiplicação e Divisão Inteiras ULA capaz de realizar a multiplicação e a divisão de forma eficiente de números inteiros. Recebe dois números inteiros (com ou sem sinal), a operação a ser realizada (multiplicação ou divisão) e um sinal para início do cálculo. Realiza a operação solicitada de forma eficiente e disponibiliza o resultado na saída, sinalizando quando ela está pronta.

5. Adição e Subtração em FP ULA capaz de realizar adição e subtração em ponto flutuante segundo o padrão IEEE 754. Esta ULA Dever haver sinalização de overflow e de underflow. Recebe dois números em ponto flutuante, a operação a ser realizada (adição ou subtração) e um sinal para início do cálculo. Realiza a operação solicitada e disponibiliza o resultado na saída, sinalizando quando ela está pronta.

6. Multiplicação em FP ULA capaz de realizar a multiplicação em ponto flutuante segundo o padrão IEEE 754. Recebe dois números em ponto flutuante e um sinal para início do cálculo. Realiza a multiplicação e disponibiliza o resultado na saída, sinalizando quando ela está pronta.

7. Divisão em FP ULA capaz de realizar a divisão em ponto flutuante segundo o padrão IEEE 754. Recebe dois números em ponto flutuante e um sinal para início do cálculo. Realiza a multiplicação e disponibiliza o resultado na saída, sinalizando quando ela está pronta.

8. Ordenador de Vetores Recebe a posição inicial de vetor armazenado numa memória e a quantidade de elementos nesse vetor. Quando sinalizado, reordena os elementos do vetor em ordem crescente, na mesma memória.

9. Controlador Programável de Interrupções Recebe sinais de interrupção de até 8 dispositivos. As interrupções que não tiverem sido mascaradas são colocadas num registrador de interrupções pendentes. O controlador seleciona a interrupção mais prioritária e ativa o sinal de interrupção da CPU. Ao receber uma solicitação externa, responde com o número do dispositivo que gerou aquela interrupção. Ao receber o sinal de término de atendimento da CPU, exclui a interrupção pendente e ativa um sinal avisando dispositivo correto.

10. Memória Cache Recebe uma requisição de leitura de um endereço na memória. Verifica se o endereço requisitado já foi armazenado na cache. Se foi, então há um acerto na cache o respectivo dado armazenado na cache é retornado. Se o endereço não está armazenado na cache, então é feita a leitura a esse endereço numa memória M1. O dado lido de M1 é armazenado na cache juntamente com seu endereço, e o dado é retornado.

Bons Livros (Recomendados)

- "Digital Design: With RTL, VHDL, and Verilog" Vahid, F. (2nd ed, Wiley, 2010); Plus "VHDL for Digital Design" / "Verilog for Digital Design" (Wiley 2007)

- "RTL HARDWARE DESIGN USING VHDL Coding for Efficiency, Portability, and Scalability" PONG P. CHU Cleveland State University"